说明:这里只是为了强调两个概念,同步和异步的含义。在数字电路中通常指的是有无同步时钟信号,如果有同步时钟,就称为同步,没有则称为异步。比如同步串行通信与异步串行通信,SDRAM中的S也是指的同步时钟的意思。在操作系统或者是多任务编程中,同步与异步指的是函数调用的返回时间,比如线程同步与线程异步。这里对相关概念进行梳理。

1. 编程中的同步与异步

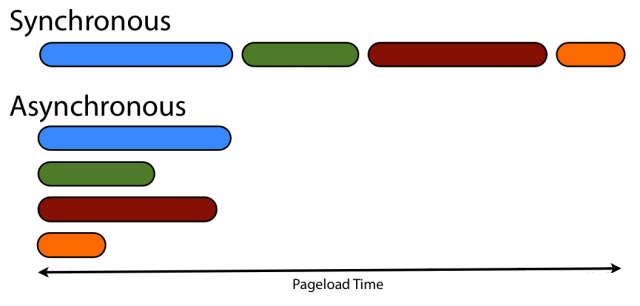

这里的同步指的就是在发出一个功能调用时,在没有得到结果之前,该调用就不返回。也就是必须一件一件事做,等前一件做完了才能做下一件事。最常见的例子就是sendmessage函数,该函数发送一个消息给某个窗口,在对方处理完消息之前,这个函数不返回。当对方处理完毕以后,该函数才把消息处理函数所返回的lresult值返回给调用者。

这里的异步指的就是当一个异步过程调用发出后,调用者不能立刻得到结果。实际处理这个调用的部件在完成后,通过状态、通知和回调来通知调用者。比如在套接字socket编程中,当一个客户端通过调用connect函数发出一个连接请求后,调用者线程立刻可以朝下运行。当连接真正建立起来以后,socket底层会发送一个消息通知该对象。

下面一段摘自同步与异步Socket

CAsyncSocket与CSocket的区别

前者是异步通信,后者是同步通信;前者是非阻塞模式,后者是阻塞模式。另外,异步非阻塞模式有时也被称为长连接,同步阻塞模式则被称为短连接。为了更明白地讲清楚两者的区别,举个例子:设想你是一位体育老师,需要测验100位同学的400米成绩。你当然不会让100位同学一起起跑,因为当同学们返回终点时,你根本来不及掐表记录各位同学的成绩。如果你每次让一位同学起跑并等待他回到终点你记下成绩后再让下一位起跑,直到所有同学都跑完。恭 喜你,你已经掌握了同步阻塞模式。你设计了一个函数,传入参数是学生号和起跑时间,返回值是到达终点的时间。你调用该函数100次,就能完成这次测验任务。这个函数是同步的,因为只要你调用它,就能得到结果;这个函数也是阻塞的,因为你一旦调用它,就必须等待,直到它给你结果,不能去干其他事情。如果你一边每隔10秒让一位同学起跑,直到所有同学出发完毕;另一边每有一个同学回到终点就记录成绩,直到所有同学都跑完。恭喜你,你已经掌握了异步非阻塞模式。你设计了两个函数,其中一个函数记录起跑时间和学生号,该函数你会主动调用100次;另一个函数记录到达时间和学生号,该函数是一个事件驱动的callback函数,当有同学到达终点时,你会被动调用。你主动调用的函数是异步的,因为你调用它,它并不会告诉你结果;这个函数也是非阻塞的,因为你一旦调用它,它就马上返回,你不用等待就可以再次调用它。但仅仅将这个函数调用100次,你并没有完成你的测验任务,你还需要被动等待调用另一个函数100次。当然,你马上就会意识到,同步阻塞模式的效率明显低于异步非阻塞模式。那么,谁还会使用同步阻塞模式呢?不错,异步模式效率高,但更麻烦,你一边要记录起跑同学的数据,一边要记录到达同学的数据,而且同学们回到终点的次序与起跑的次序并不相同,所以你还要不停地在你的成绩册上查找学生号。忙乱之 中你往往会张冠李戴。

你可能会想出更聪明的办法:你带了很多块秒表,让同学们分组互相测验。恭喜你!你已经掌握了多线 程同步模式!

每个拿秒表的同学都可以独立调用你的同步函数,这样既不容易出错,效率也大大提高,只要秒表足够 多,同步的效率也能达到甚至超过异步。可以理解,你现的问题可能是:既然多线程同步既快又好,异步模式还有存在的必要吗?

很遗憾,异步模式依然非常重要,因为在很多情况下,你拿不出很多秒表。你需要通信的对端系统可能

只允许你建立一个SOCKET连接,很多金融、电信行业的大型业务系统都如此要求。

现在,你应该已经明白了:CAsyncSocket用于在少量连接时,处理大批量无步骤依赖性的业务。CSocket

用于处理步骤依赖性业务,或在可多连接时配合多线程使用。

2. 数字电路中的同步与异步

同步电路是说电路里的时钟相互之间是同步的,同步的含义不只局限于同一个CLOCK,而是容许有多个CLOCK,这些CLOCK的周期有倍数关系并且相互之间的相位关系是固定的就可以,比如, 10ns, 5ns, 2.5ns 三个CLOCK的电路是同步电路。我们现在的综合,STA都是针对同步电路的。

异步电路是指CLOCK之间没有倍数关系或者相互之间的相位关系不是固定的,比如5ns, 3ns 两个CLOCK是异步的。异步电路无法作真正意义上的综合及STA,如果在同步电路里夹杂有异步电路,就set_flase_path。所以异步电路只有靠仿真来检查电路正确与否。

异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻 是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。也就是说一个时刻允许一个输入发生变化,以避免输入信号之间造成的竞争冒险。

同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所 有的状态变化都是在时钟的上升沿(或下降沿)完成的。比如D触发器,当上升延到来时,寄存器把D端的电平传到Q输出端。

特别推荐:推荐给你一本必须人手一本的《电子工程师参考手册》,扫描下面的二维码关注微信公众号(易监控),回复“获取资料”自动下载领取。

已有 0 位网友参与,快来吐槽:

发表评论